MMX (Multimedia Extensions)

Designa o conjunto de 57 instruções introduzidas nos processadores Intel e outros processadores compatíveis no início de 1997 para a consulta de dados multimédia. Permitem um uso eficaz do processador para operações específicas de multimédia como processamento digital de sinal.

Designa o conjunto de 57 instruções introduzidas nos processadores Intel e outros processadores compatíveis no início de 1997 para a consulta de dados multimédia. Permitem um uso eficaz do processador para operações específicas de multimédia como processamento digital de sinal.

Apenas software escrito para chamar especificamente essas instruções pode fazer uso dessa potencialidade e, com efeito, não foi feito um grande esforço por parte de empresas criadoras de compiladores de várias linguagens para a plataforma x86 em adaptar os seus produtos para fazer uso extensivo destas instruções. Muito recentemente a Intel admitiu tratar-se de um flop o lançamento destes chips visto não terem tido um suporte em termos de software comercial como pano de fundo.

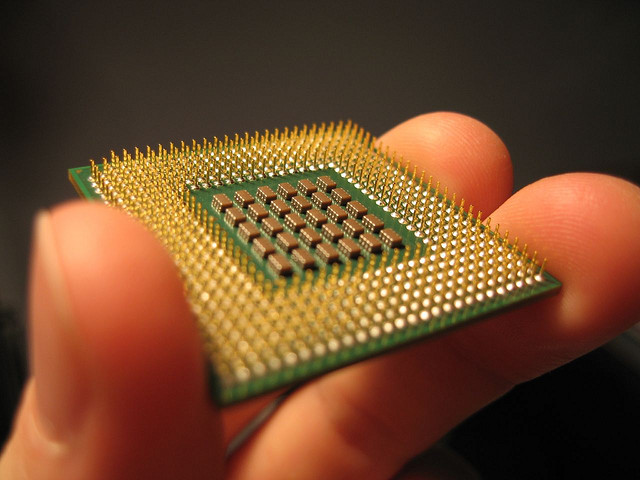

Overclocking

O overclock é um processo no qual a velocidade de componentes específicos de um computador são manualmente aumentadas, através de configurações e instruções diretas para o hardware. A melhora de desempenho que é atingida após o processo pode variar, mas entusiastas conseguem fazer componentes antigos funcionarem como os últimos lançamentos, assim como fazem as peças mais modernas superarem os limites da tecnologia atual.

Hyper-Threading

CISC

RISC

CISC vs RISC

A memória, hoje em dia, é rápida e barata; qualquer pessoa que tenha instalado recentemente um programa da Microsoft sabe que muitas das companhias que desenvolvem software já não têm em consideração as limitações de memória. Assim, as preocupações com o tamanho do código que deram origem ao vasto conjunto de instruções da arquitectura CISC já não existem. De facto, os processadores da era pós-RISC têm conjuntos de instruções cada vez maiores de um tamanho e diversidade sem precedentes, e ninguém pensa duas vezes no efeito que isso provoca no uso da memória.

Compiladores

O desenvolvimento dos compiladores sofreu um tremendo avanço nos últimos anos. De facto, chegou a um ponto tal que a próxima geração de arquitecturas (como o IA-64 ou Merced da Intel) dependem apenas do compilador para ordenar as instruções tendo em vista a máxima taxa de instruções executadas. Os compiladores RISC tentam manter os operandos em registos por forma a poderem usar simples instruções registo-registo. Os compiladores tradicionais, por outro lado, tentam descobrir o modo de endereçamento ideal e o menor formato de instrução para fazerem os acessos à memória. Em geral, os programadores de compiladores RISC preferem o modelo de execução registo-registo de forma que os compiladores possam manter os operandos que vão ser reutilizados em registos, em vez de repetirem os acessos à memória de cada vez que é necessário um operando. Usam, por isso, LOAD’s e STORE’s para aceder à memória para que os operandos não sejam, implicitamente, rejeitados após terminada a execução de uma determinada instrução, como acontece nas arquitecturas que utilizam um modelo de execução memória-memória.

Luís Martins nº14 12ºF

Pedro Silva nº18 12ºF

Luís Martins nº14 12ºF

Pedro Silva nº18 12ºF

Sem comentários:

Enviar um comentário